#### UNIVERSITY OF BRISTOL

# Practice Paper 1B (practical section) School of Computer Science

First In-class Test for the Degree of Master of Science in Computer Science (conversion)

### COMSM1302 Overview of Computer Architecture

## TIME ALLOWED: 2 Hours

This section contains **four** questions. **All** questions will be marked.

The maximum for this section is **50 marks**.

#### Other Instructions

- 1. You are not permitted to visit any web sites other than those in the "In-class test 1" sidebar of the unit Blackboard page.

- 2. You are permitted to use the Calculator app in Basic or Advanced mode only, or the KCalc app in Simple or Science mode only.

- 3. You are not permitted the use of physical calculators.

- 4. You are permitted the use of the exam version of Logisim linked on the unit Blackboard page, and no other versions of Logisim.

- 5. This is not a real exam paper.

#### TURN OVER ONLY WHEN TOLD TO BEGIN WORK

For each question, build the circuit within the Logisim skeleton file provided. Each question subcircuit will already contain every input and output pin required. The components permitted to build the circuit are listed at the end of each question — do **not** use any components other than those explicitly permitted and those in the "Wiring" folder (e.g. constants and splitters). You may create further subcircuits, but they should only consist of permitted components for that question. Your final design (using any extra subcircuits you've built) should be built in the given subcircuit e.g. your design for Question 1 should be built with the Q1 subcircuit.

Full marks will be given to circuits that display the correct behaviour while only using permitted components. You are not required to use all permitted components. Partial marks will be available. Complexity and neatness will not be marked, unless otherwise stated.

In the actual test, you should submit your completed Logisim file to the "In-Class Test 1 (Practical component) submission point" on Blackboard. Multiple submissions are allowed, but only the last one will be marked.

#### Question 1 (10 marks)

Create a circuit that implements the Boolean expression:

$$(A \lor B) \land \neg (A \land B \land C) \land \neg C$$

Permitted components: 2-input AND gates, 2-input OR gates, and NOT gates.

#### Question 2 (10 marks)

Create a circuit that implements the below truth table, using at most 8 logic gates. Partial credit will be given for any solution that implements the truth table with more than 8 gates, depending on the number of gates used.

| A | В | $\mathbf{C}$ | D | Out |

|---|---|--------------|---|-----|

| 0 | 0 | 0            | 0 | 1   |

| 0 | 0 | 0            | 1 | 0   |

| 0 | 0 | 1            | 0 | 1   |

| 0 | 0 | 1            | 1 | 0   |

| 0 | 1 | 0            | 0 | 1   |

| 0 | 1 | 0            | 1 | 0   |

| 0 | 1 | 1            | 0 | 0   |

| 0 | 1 | 1            | 1 | 0   |

| 1 | 0 | 0            | 0 | 1   |

| 1 | 0 | 0            | 1 | 0   |

| 1 | 0 | 1            | 0 | 1   |

| 1 | 0 | 1            | 1 | 1   |

| 1 | 1 | 0            | 0 | 1   |

| 1 | 1 | 0            | 1 | 0   |

| 1 | 1 | 1            | 0 | 1   |

| 1 | 1 | 1            | 1 | 1   |

**Permitted components:** Any logic gates with 2 or fewer inputs.

#### Question 3 (15 marks)

Create a circuit that implements a 4-bit full adder with 4-bit inputs A and B, 4-bit output Sum, 1-bit carry input  $C\_in$ , and 1-bit carry output  $C\_out$ .

**Permitted components:** Any logic gates with 2 or fewer inputs.

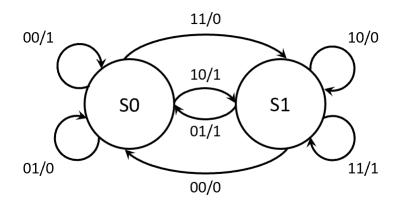

#### Question 4 (15 marks)

Create a circuit that implements the Mealy machine described by the below state transition diagram. Your circuit should update the 1-bit outputs Out and  $Current\_state$  on the falling-edge of a clock, given the 2-bit input In.

Permitted components: All components are permitted.